Biography

Jianxin Chen is a Quantum Scientist at Alibaba Group’s global research institute, DAMO Academy. He holds the position of Head of Quantum Computer Systems within the Quantum Laboratory, a division of DAMO Academy. Jianxin earned both his Bachelor’s and Ph.D. degrees in computer science from Tsinghua University. Prior to joining Alibaba, he served as a Hartree fellow at the Joint Center for Quantum Information and Computer Science at the University of Maryland.

Jianxin’s primary research focus centers on the development of a robust and fault-tolerant quantum computer system. To date, he has authored and published over 60 research papers in top journals such as PRL, PRX Quantum, Nature Computational Science, as well as top conferences such as Quantum Information Processing and ASPLOS. Jianxin is an IEEE senior member and he has actively contributed to the program committees of prestigious conferences such as QIP (Quantum Information Processing), TQC (The Theory of Quantum Computation, Communication, and Cryptography), and IEEE Quantum Week.

- Quantum Computer Architecture

- Fault-tolerant Quantum Computing

- Quantum Hardware-software Co-Design

PhD in Computer Science, 2010

Tsinghua University

MS in Computer Science, 2010

Tsinghua University

BEng in Computer Science, 2005

Tsinghua University

Experience

Responsibilities include:

- Strategic Planning

- Technical Development

- Team Management and Development

Projects

Featured Publications

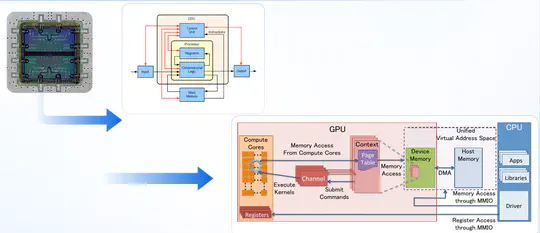

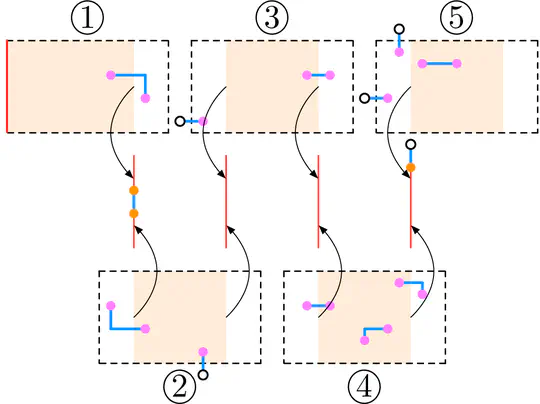

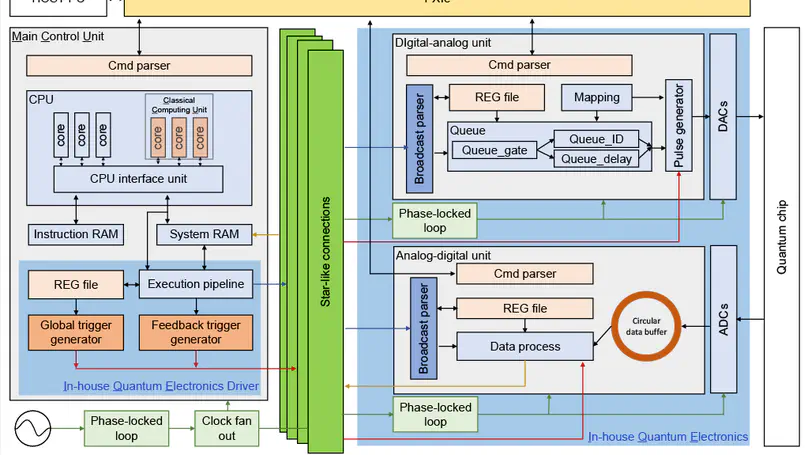

Scaling bottlenecks the making of digital quantum computers, posing challenges from both the quantum and the classical components. We present a classical architecture to cope with a comprehensive list of the latter challenges all at once, and implement it fully in an end-to-end system by integrating a multi-core RISC-V CPU with our in-house control electronics. Our architecture enables scalable, high-precision control of large quantum processors and accommodates evolving requirements of quantum hardware. A central feature is a microarchitecture executing quantum operations in parallel on arbitrary predefined qubit groups. Another key feature is a reconfigurable quantum instruction set that supports easy qubit re-grouping and instructions extensions. As a demonstration, we implement the surface code quantum computing workflow. Our design, for the first time, reduces instruction issuing and transmission costs to constants, which do not scale with the number of qubits, without adding any overheads in decoding or dispatching. Our system uses a dedicated general-purpose CPU for both qubit control and classical computation, including syndrome decoding. Implementing recent theoretical proposals as decoding firmware that parallelizes general inner decoders, we can achieve unprecedented decoding capabilities of up to distances 47 and 67 with the currently available systems-on-chips for physical error rate p = 0.001 and p = 0.0001, respectively, all in just 1 µs.

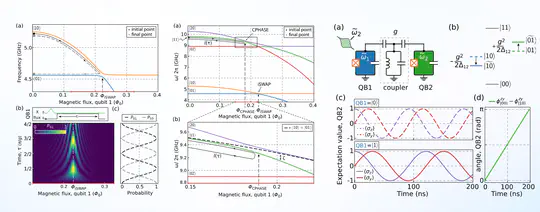

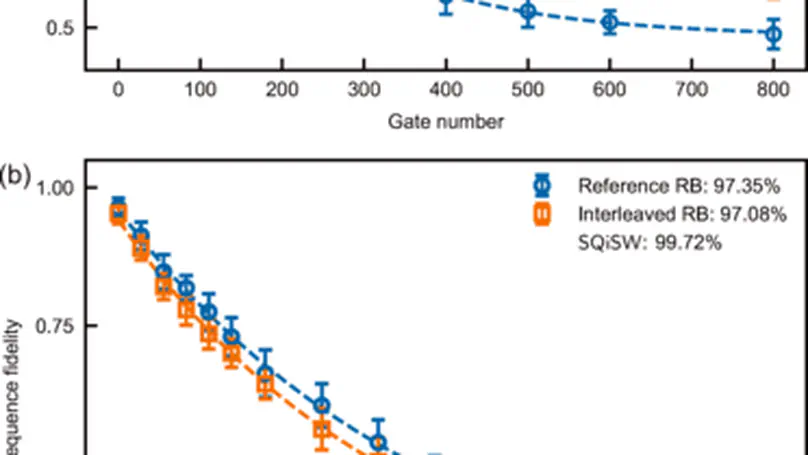

A quantum instruction set is where quantum hardware and software meet. We develop new characterization and compilation techniques for non-Clifford gates to accurately evaluate different quantum instruction set designs. We specifically apply them to our fluxonium processor that supports mainstream instruction iSWAP by calibrating and characterizing its square root SQiSW. We measure a gate fidelity of up to 99.72% with an average of 99.31% and realize Haar random two-qubit gates using SQiSW with an average fidelity of 96.38%. This is an average error reduction of 41% for the former and a 50% reduction for the latter compared to using iSWAP on the same processor. This shows designing the quantum instruction set consisting of SQiSW and single-qubit gates on such platforms leads to a performance boost at almost no cost.

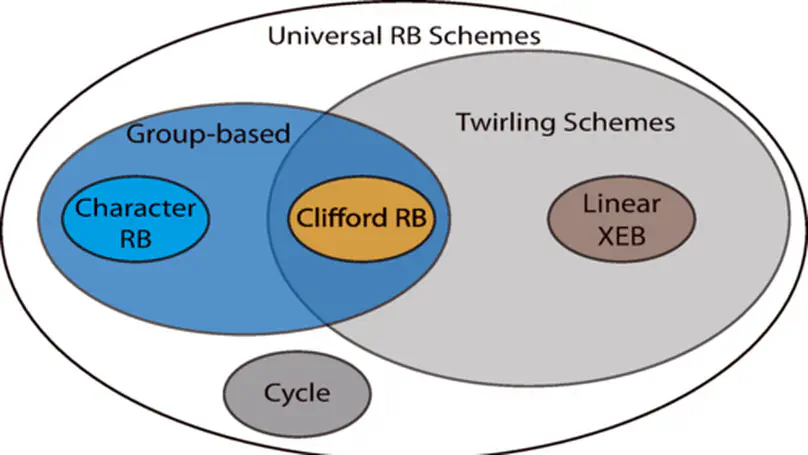

Randomized benchmarking (RB) is the gold standard for experimentally evaluating the quality of quantum operations. The current framework for RB is centered on groups and their representations, but this can be problematic. For example, Clifford circuits need up to $O(n^2)$ gates, and thus Clifford RB cannot scale to larger devices. Attempts to remedy this include new schemes such as linear cross-entropy benchmarking (XEB), cycle benchmarking, and non-uniform RB, but they do not fall within the group-based RB framework. In this work, we formulate the \emph{universal randomized benchmarking (URB) framework} which does away with the group structure and also replaces the recovery gate plus measurement component with a general ``post-processing’’ POVM. Not only does this framework cover most of the existing benchmarking schemes, but it also gives the language for and helps inspire the formulation of new schemes. We specifically consider a class of URB schemes called \emph{twirling schemes}. For twirling schemes, the post-processing POVM approximately factorizes into an intermediate channel, inverting maps, and a final measurement. This leads us to study the twirling map corresponding to the gate ensemble specified by the scheme. We prove that if this twirling map is strictly within unit distance of the Haar twirling map in induced diamond norm, the probability of measurement as a function of gate length is a single exponential decay up to small error terms. The core technical tool we use is the matrix perturbation theory of linear operators on quantum channels.

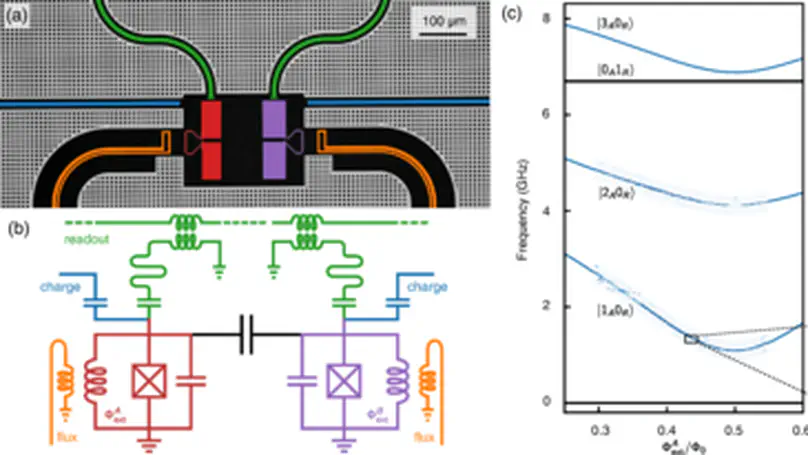

Superconducting qubits provide a promising path toward building large-scale quantum computers. The simple and robust transmon qubit has been the leading platform, achieving multiple milestones. However, fault-tolerant quantum computing calls for qubit operations at error rates significantly lower than those exhibited in the state of the art. Consequently, alternative superconducting qubits with better error protection have attracted increasing interest. Among them, fluxonium is a particularly promising candidate, featuring large anharmonicity and long coherence times. Here, we engineer a fluxonium-based quantum processor that integrates high qubit coherence, fast frequency tunability, and individual-qubit addressability for reset, readout, and gates. With simple and fast gate schemes, we achieve an average single-qubit gate fidelity of 99.97% and a two-qubit gate fidelity of up to 99.72%. This performance is comparable to the highest values reported in the literature of superconducting circuits. Thus our work, within the realm of superconducting qubits, reveals an alternative qubit platform that is competitive with the transmon system.

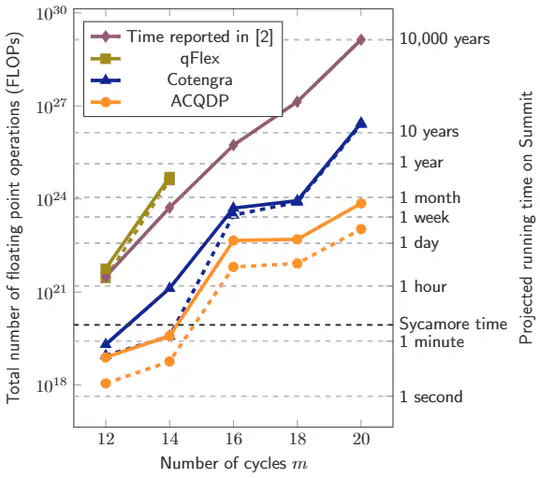

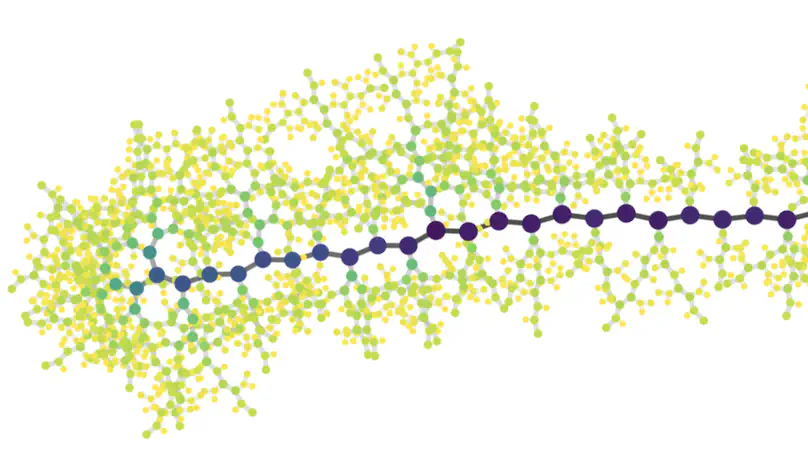

We develop an algorithmic framework for contracting tensor networks and demonstrate its power by classically simulating quantum computation of sizes previously deemed out of reach. Our main contribution, index slicing, is a method that efficiently parallelizes the contraction by breaking it down into much smaller and identically structured subtasks, which can then be executed in parallel without dependencies. We benchmark our algorithm on a class of random quantum circuits, achieving greater than 105 times acceleration over the original estimate of the simulation cost. We then demonstrate applications of the simulation framework for aiding the development of quantum algorithms and quantum error correction. As tensor networks are widely used in computational science, our simulation framework may find further applications.